Verilog基础语法部分

模块(module)定义

1

2

3

4

5

6

7

8

module fenpin(input clk_in,output clk_out);

reg c_out=0;

assign clk_out = c_out;

always @ (posedge clk_in)

begin

c_out = ~c_out;

end

endmodule

单元说明

- 时序逻辑部分在

always块的内部,在always块中只能对寄存器变量赋值 -

对端口或其他wire型变量的赋值,必须在

always块的外部使用assign语句 -

寄存器必须在时钟驱动下(有效边沿)才能改变其内容,编程决定

parameter可以定义宏,可以在不同的module中调用- 用

#(xxx,xxx)可以对宏重新定义

- 用

- 存储器是一个寄存器数组

reg [2,0] memory1[3,0]表示3位位宽(不注明就只为1位),有4个存储单元memory1[0:3]=0,速度非常快的大量赋值

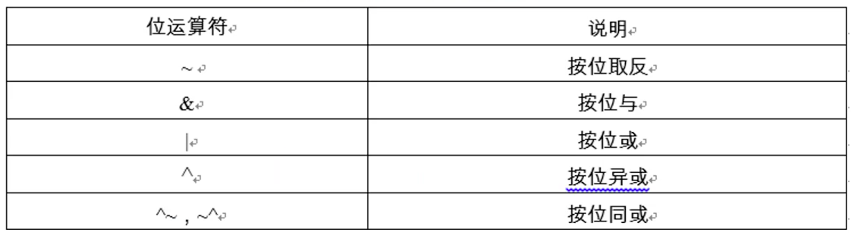

运算

- 整数除法,结果略去小数部分,结果的符号位采用模运算符中第一个操作符的符号

-10%3=-1、11%-3=2

- 逻辑运算只区分真假,

4'h01和4'ha1都表示真- 注意:

<=在形如b<=i_a;中,表示的是非阻塞的赋值

- 注意:

- 算数运算符同

c++ - 等式运算符

===全等!==不全等

- 缩减运算符

c=%b即为c=((b[0]&b[1])&b[2])&b[3]

-

移位同数电

-

条件运算符(同

c++)cond?true_cond:false_cond

结构说明语句

always- 有点像GUI中的事件监听

always @ (clk),只要clk发生变化就触发always @ (posedge clk),clk上升就触发always @ (negedge clk),clk下降就触发always @ (negedge clk1 or posedge clk2),clk上升或下降就触发always @ (*)只要模块的任何输入信号变化了都触发

- 有点像GUI中的事件监听

initial- 有点像构造函数

条件语句

-

if- 同

C++用法,但Verilog没有花括号括起多条语句而是用begin和end间隔开

- 同

-

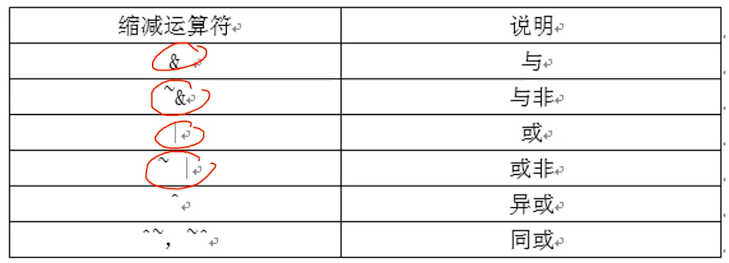

case(每一位都确定)、casez(忽略高阻态)、casex(忽略高阻态和不定态)- 有点像

switch,但是在每一个case尾部不需要加break case尾部加上endcasecase所有表达式的位宽必须相等

- 有点像

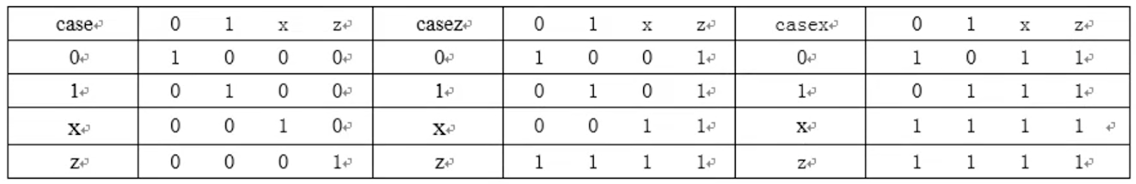

循环语句

forever,始终执行repeat (num),执行num次的循环while,直到某条件不满足,以end结尾

注意:循环次数必须是能够确定的,代码才有效,下面是一个反例

for(ex1,ex2,ex3),与c++中的for类似

OpenMIPS

- 32个通用寄存器

$0$\to$$31

Vivado初步部分

后续更新

2019.12.17

《自己动手写CPU》第四、六章

五级流水图——P61

blackModel